Akademie věd České republiky Ústav teorie informace a automatizace AV ČR, v.v.i.

# Computation and Communication Blocks for Xilinx Kintex7 FPGA with UTIA EdkDSP Accelerators. Vivado 2013.4 Designs with SW Demos.

Jiří Kadlec

<u>kadlec@utia.cas.cz</u> phone: +420 2 6605 2216 UTIA AV CR, v.v.i.

Revision history:

| Rev. | Date       | Author      | Description                                                                                                  |

|------|------------|-------------|--------------------------------------------------------------------------------------------------------------|

| 1    | 17.11.2014 | Jiří Kadlec | Description of precompiled Vivado 2013.4<br>Kintex7 designs with EdkDSP accelerators and<br>examples of use. |

| 2    | 13.12.2014 | Jiří Kadlec | Updated for EdkDSP accelerator clock 175<br>MHz                                                              |

|      |            |             |                                                                                                              |

|      |            |             |                                                                                                              |

|      |            |             |                                                                                                              |

|      |            |             |                                                                                                              |

Acknowledgements:

This work has been partially supported by the Artemis JU project ALMARVI "Algorithms, Design Methods, and Many-Core Execution Platform for Low-Power Massive Data-Rate Video and Image Processing", project number Artemis JU 621439 and 7H14004 (Ministry of Education Youth and Sports of the Czech Republic [6].

| Computation and Communication Blocks for Xilinx Kintex7 FPGA                  |      |

|-------------------------------------------------------------------------------|------|

| with UTIA EdkDSP Accelerators. Vivado 2013.4 Designs with SW Demos            | 1    |

| 1. Summary                                                                    |      |

| 1.1 Communication and Computation blocks for Video and Image Processing       | 3    |

| 1.2 What is included                                                          |      |

| 2. Description of EdkDSP Accelerators and Demos                               | 5    |

| 2.1 Description of EdkDSP accelerators and evaluation designs                 |      |

| 2.2 Resources used by the designs                                             | 9    |

| 2.3 Use of external DDR3 memory                                               | . 10 |

| 2.4 Re-programmability of EdkDSP accelerators                                 | . 10 |

| 2.5 Debug of evaluation designs with EdkDSP accelerators                      |      |

| 3. Installation and use of the evaluation package                             |      |

| 3.1 Import of precompiled HW and SW projects into Xilinx SDK 2013.4           | . 11 |

| 3.2 Evaluation of demo projects                                               | . 18 |

| 3.3 Ethernet point to point connection with PC                                | . 22 |

| 3.4 Boot of the bitstream                                                     | . 22 |

| 3.5 Boot of the application                                                   | . 22 |

| 3.6 Use of the C compiler for the EdkDSP firmware with download from Ethernet | . 35 |

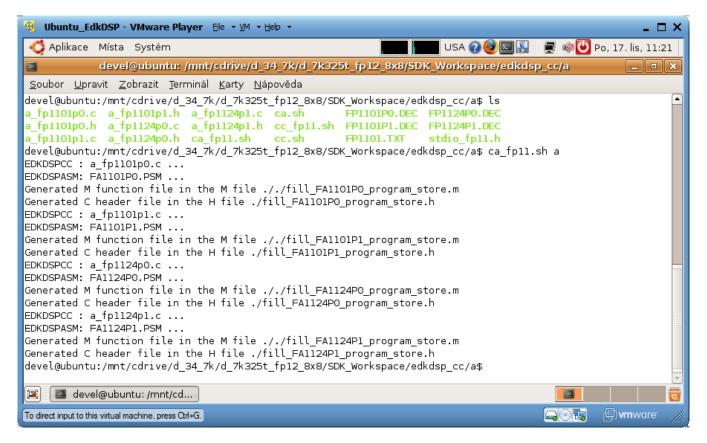

| 3.7 Use of the C compiler for the EdkDSP firmware witout Ethernet             | . 49 |

| 4. References                                                                 | . 55 |

| 5. Evaluation version of Vivado 2013.4 Kintex7 designs                        | . 56 |

| 6. Release version of Vivado 2013.4 Kintex7 designs for Almarvi project       |      |

| partners                                                                      |      |

| 7. Release version of Vivado 2013.4 Kintex7 designs                           | . 59 |

| Disclaimer                                                                    | . 61 |

2/61

http://zs.utia.cas.cz

## 1. Summary

## 1.1 Communication and Computation blocks for Video and Image Processing

This application note describes precompiled Vivado 2013.4 Kintex7 designs with the floating point EdkDSP accelerators and examples of use of basic communication and computation blocks used in the video processing and image processing applications. The MicroBlaze SoC design with the AXI bus is based on the Xilinx BIST (build in self-test) provided by Xilinx for the Kintex7 KC705 board and the Vivado 2014.3 design flow. The network HW controller is supporting 1Gbit/100Mbit/10Mbit standards with HW DMA and a SW stack based on the IwIP library described in the Xilinx application note XAPP1026 [3], [4]. The MicroBlaze processor is controlling 8 EdkDSP floating point accelerators. Each accelerator is organised as 8xSIMD reconfigurable data path, controlled by a PicoBlaze6 controller. This evaluation package is provided by UTIA for the Xilinx KC705 board with the 28nm Kintex7 xc7k325t-2 FPGA part. This application note explains how to install and use the demonstrator on Windows7, (32 or 64 bit) and Xilinx KC705 board [1], [2]. The evaluation package can be also installed and used on PC running Linux (32 or 64 bit) or Win XP (32 or 64 bit) with the corresponding Xilinx SDK 2013.4.

These key features are demonstrated:

- WWW server running on Kintex7 KC705 board with the IwIP stack running in RAW mode or SOCKET mode with the Xilkernel support of POSIX compatible threads.

- TFTP server running on Kintex7 KC705 board with the IwIP stack running in RAW mode or SOCKET mode.

- RAM based file system with files in the DDR3 memory on the KC705 board.

- 8 reprogrammable floating point accelerators for local embedded computing on the Kintex7 28nm chip.

- Demo implementation of an adaptive acoustic noise cancellation on 1 of 8 accelerators is computing the recursive adaptive LMS algorithm for identification of regression filter with 2000 coefficients in single precision floating point arithmetic with this sustained performance

- o 1012,0 MFLOP/s on a single 175 MHz (8xSIMD) EdkDSP accelerator (only 1 of the 8 units is used)

- 7,6 MFLOP/s on the 100 MHz MicroBlaze processor with the floating point HW unit

- The EdkDSP accelerators can be reprogrammed by the firmware. The programming is possible in C with the use of the UTIA EDKDSP C compiler. Accelerators can be programmed with two firmware programs. Designs can swap in the real time the firmware in only few clock cycles in the runtime.

- The alternative firmware can be downloaded to the EdkDSP accelerators from the internet in parallel with the execution of the current firmware. This is demonstrated by the download of firmware by the TFTP server and by swap of the firmware for the FIR filter room-response to the firmware for the adaptive LMS identification of the filter coefficients in the acoustic noise cancellation demo.

- The EdkDSP accelerator is providing single-precision floating point results bit-exact identical to the reference software implementations running on the MicroBlaze with the Xilinx HW single precision floating point unit.

- Single 175 MHz (8xSIMD) EdkDSP accelerator is 132x faster than computation on the performance optimized 100 MHz MicroBlaze with HW floating point unit, in the presented case of the 2000 tap adaptive LMS filter.

- The floating point 2000 tap coefficients FIR filter (acoustics room model) is computed by single 175 MHz (8xSIMD) EdkDSP accelerator with the floating point performance of 1403 MFLOP/s. The peak performance (only theoretical) of a single 175 MHz (8xSIMD) EdkDSP accelerator is 2,8 GFLOP/s.

- The peak performance of eight 175 MHz (8xSIMD) EdkDSP accelerators implemented in this demo design is 22,4 GFLOP/s (this is only theoretical peek figure).

- This evaluation package presents two (8xSIMD) EdkDSP accelerator families: one family without pipelined floating point divider data path and one family with a single pipelined floating point divider data path. The members of both families differ by size and by supported vector floating point operations.

- The floating point applications are scheduled inside of the EdkDSP accelerator by the Xilinx PicoBlaze6 processor [5]. Each PicoBlaze6 firmware program has maximal size of 4096 (18 bit wide words).

3/61

0

## **1.2 What is included**

The evaluation package includes precompiled Vivado 2013.4 Kintex7 designs with floating point EdkDSP accelerators and SW examples of communication and computation in form of Xilinx SDK 2013.4 SW projects for Windows 7 (32 or 64bit) or a PC running Linux (32 or 64 bit) or Win XP (32 or 64 bit) with the corresponding installation of Xilinx SDK 2013.4:

- 8 evaluation versions of precompiled Kintex7 designs. Each design contains one MicroBlaze and eight instances of the EdkDSP accelerators. Each accelerator has 8xSIMD floating point data paths and programmable PicoBlaze6 controller for scheduling of floating point vector operations in the accelerator. The MicroBlaze works with 100 MHz system clock and EdkDSP accelerators use 175 MHz clock. The Microblaze processor works with 1 Gb Ethernet with DMA controller and 1 GB DDR3 memory. Designs are compiled in Xilinx Vivado 2013.4.

- UTIA is providing source code for the demo applications and SW projects for the Xilinx SDK 2013.4. These source code projects are compiled with the UTIA library libwal.a serving for the EdkDSP communication and the library libmfsimage.a with the initial file system supporting the simple www server GUI.

- The included evaluation versions of the UTIA EdkDSP accelerators have HW limitation of maximal number of performed vector operations.

- The UTIA EDKDSPC C compiler is provided as 4 binary applications for Ubuntu in the VMware Player.

- The firmware for accelerators is provided in source code and also in format of binary files to enable the initial evaluation of the EdkDSP accelerators without the need to install the EDKDSPCC C compiler.

- UTIA partners of the Artemis Almarvi [6] project can get from UTIA the release version of Vivado 2013.4 HW design projects with the evaluation versions of the EdkDSP accelerators (in the Vivado 2013.4 IP netlist format) for free. See chapter 6 for specification of deliverables for the Artemis Almarvi [6] project partners with license details.

- Release versions of Vivado 2013.4 HW design projects and release version of EdkDSP accelerators for the Xilinx KC705 board is offered by UTIA. All customers can order and buy from UTIA the release version of this demo. It includes the Vivado 2013.4 HW design projects with the EdkDSP accelerators (in the Vivado 2013.4 IP netlist format) with the HW limitation of maximal number of performed vector operations removed. See sections 7 of this application note for specification of deliverables and license details.

4/61

## 2. Description of EdkDSP Accelerators and Demos

## 2.1 Description of EdkDSP accelerators and evaluation designs

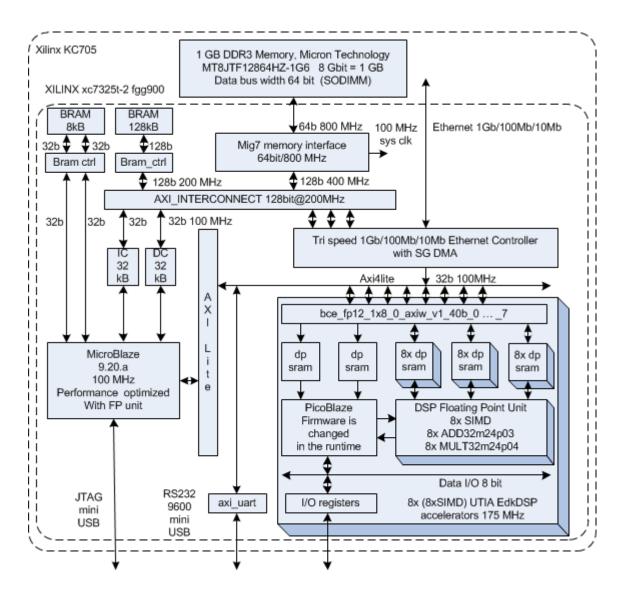

This application note describes how to set-up and use of 8 HW designs running on one MicroBlaze processor, each design with eight (8xSIMD) EdkDSP accelerators on Xilinx KC705 board. See Figure 1 and Figure 2.

Demonstrators serve for evaluation of the communication and computation processor infrastructure. Utia is providing two floating point accelerator families for the Xilinx Kintex7 xc7k325t-2 part:

- bce\_fp11\_1x8\_0\_axiw\_v1\_[10|20|30|40]\_b ibs a family of four versions of floating point EdkDSP accelerators with 8 SIMD data paths.

- bce\_fp12\_1x8\_0\_axiw\_v1\_[10|20|30|40]\_b is similar family of four versions of floating point EdkDSP accelerators with 8 SIMD data paths extended by a pipelined floating point division (FPDIV) in a single data path.

The four grades [10|20|30|40] of the EdkDSP accelerator differ in HW-supported vector computing capabilities:

The area optimized accelerators bce\_fp11\_1x8\_0\_axiw\_v1\_10\_b and bce\_fp12\_1x8\_0\_axiw\_v1\_10\_b perform vector floating point operations FPADD, FPSUB in 8 SIMD data paths.

The accelerators bce\_fp11\_1x8\_0\_axiw\_v1\_20\_b and bce\_fp12\_1x8\_0\_axiw\_v1\_20\_b perform vector floating point operations FPADD, FPSUB in 8 SIMD data paths plus the vector floating point MAC operations in 8 SIMD data paths for length of the vector 1 up to 10. These accelerators can be used in applications like floating point matrix multiplication with row and column dimensions <= 10.

The accelerators bce\_fp11\_1x8\_0\_axiw\_v1\_30\_b and bce\_fp12\_1x8\_0\_axiw\_v1\_30\_b support identical operations as the bce\_fp11\_1x8\_0\_axiw\_v1\_20\_b and bce\_fp12\_1x8\_0\_axiw\_v1\_20\_b plus the floating point vector by vector dot products performed in 8 SIMD data paths. It is optimized for parallel computation of up to 8 FIR or LMS filters, each with size up to 255 coefficients. It is also effective in case of floating point matrix by matrix multiplications, where one of the dimensions is large (in the range from 11 to 255).

Finally, the accelerators bce\_fp11\_1x8\_0\_axiw\_v1\_40\_b and bce\_fp12\_1x8\_0\_axiw\_v1\_40\_b support identical operations as the bce\_fp11\_1x8\_0\_axiw\_v1\_30\_b and bce\_fp12\_1x8\_0\_axiw\_v1\_30\_b plus an additional HW support of dot product. It is computed in 8 data paths with the HW supported wind-up into single scalar result.

The bce\_fp11 versions of 8xSIMD accelerators has no support for pipelined vector floating point division and it is suitable for applications like FIR filters or adaptive LMS filters with no need for floating point division.

The bce\_fp12 versions of 8xSIMD accelerators are larger in comparison to the bce\_fp11 equivalents and support in a single data path the pipelined vector floating point division. Accelerators are suitable for applications like adaptive normalised NLMS filters and the square root free versions of adaptive RLS QR filters and adaptive RLS LATTICE filters.

See Figure 3 and Figure 4 for the resources used by the evaluation designs included in this package.

Akademie věd České republiky

Ústav teorie informace a automatizace AV ČR, v.v.i.

Photo 1: Demonstration of 1 Gb ethernet, www server and TFTP server with 8x (8xSIMD) EdkDSP floating point accelerators on Xilinx KC705 board with Kintex7 FPGA.

Ten HW designs precompiled in Vivado 2013.4 combine MicroBlaze and eight 8xSIMD EdkDSP accelerators. All designs demonstrate use of single instance of 8xSIMD EdkDSP floating point accelerator on 32bit AXI-lite bus of the Xilinx MicroBlaze soft-core processor on the Xilinx Kintex7 KC705 FPGA board with system clock of MicroBlaze 100 MHz and EdkDSP accelerators 175 MHz. See Figure 2.

Common properties of precompiled Vivado 2013.4 evaluation designs:

- The EdkDSP floating point accelerators are reconfigurable during runtime by change of firmware.

- All HW evaluation designs have been compiled in Xilinx VIVADO 2013.4 with SW projects for SDK 2013.4.

Presented HW accelerators can results in better POWER per MFLOPS ratio for certain class of DSP applications in comparison to the computation on MicroBlaze with HW floating point support.

The demonstrator includes source code of set of SW demos prepared for easy import of projects and compilation in the Xilinx SDK 2013.4.

6/61

Figure 1: Key building blocks of the Kintex demonstrator with 8 EdkDSP accelerators.

Figure 1 describes the the key building blocks of the design. It is SoC with MicroBlaze, Tri speed ethernet (1Gb/100Mb/10Mb) with SG central DMA and eight EdkDSP accelerators. Each accelerator works with 8xSIMD floating point unit controlled by a reprogrammable PicoBlaze6 controller. There are in total nine programmable processors, all capable of HW supported parallel floating point computation.

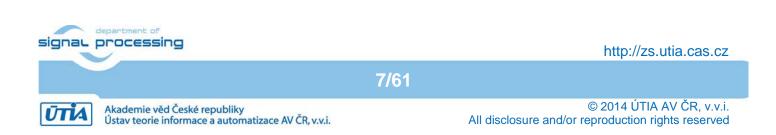

Demo designs are based on the modified Vivado 2013.4 KC705 BIST (built-in self-test) reference design from Xilinx. See the complete design in the IP Integrator on Figure 2.

#### Figure 2: Design with 8 EdkDSP accelerators in Xilinx Vivado; 2013.4 IP Integrator.

Figure 2 describes the SoC with MicroBlaze, 1Gb Ethernet and eight EdkDSP accelerators. The design is based on the Vivado 2013.4 KC705 BIST (built-in self-test) reference design from Xilinx.

The initial MicroBlaze boot block RAM is set to 32 KB. The internal program and data RAM memory is set to 128 KB size. Data width of this AXI interfaced memory is set to 128 bit to support burst operations.

The 8 EdkDSP (8xSIMD) floating point accelerators are memory mapped on the 32 bit AXI-lite bus. Each accelerator has reserved 1 MB of address space. See Figure 3 and Figure 4 for the resources used by the designs.

## **2.2** *Resources used by the designs*

The resources used by the 8 presented designs are summarised in Figure 3 and Figure 4.

| 7k325t-2    | fp  | fp  | fp   | fp   | fp  | Design size |      | Performance |         |         |

|-------------|-----|-----|------|------|-----|-------------|------|-------------|---------|---------|

|             | Add |     | Dot  | S8   |     | FFs         | LUTs | Bram        | LMS     | FIR     |

|             | Mul | Mac | Prod | Prod | Div | %           | %    | No (of)     | Mflop/s | Mflop/s |

| kc705_bist  |     |     |      |      |     | 7           | 15   | 63 (445)    |         |         |

| (6x)        |     |     |      |      |     |             |      |             |         |         |

| fp11_1x8_10 | 8x  |     |      |      |     | 15          | 41   | 303 (445)   |         |         |

| (8x)        |     |     |      |      |     |             |      |             |         |         |

| fp11_1x8_20 | 8x  | 8x  |      |      |     | 17          | 44   | 303 (445)   |         |         |

| (8x)        |     |     |      |      |     |             |      |             |         |         |

| fp11_1x8_30 | 8x  | 8x  | 8x   |      |     | 19          | 51   | 303 (445)   |         |         |

| (8x)        |     |     |      |      |     |             |      |             | (8x)    | (8x)    |

| fp11_1x8_40 | 8x  | 8x  | 8x   | 1x   |     | 19          | 52   | 303 (445)   | 1012    | 1403    |

Figure 3: Resources used by MicroBlaze and 8x (8xSIMD) EdkDSP, no FP division

| 7k325t-2    | fp  | fp  | fp   | fp   | fp  | Design size |      | Performance |         |         |

|-------------|-----|-----|------|------|-----|-------------|------|-------------|---------|---------|

|             | Add |     | Dot  | S8   |     | FFs         | LUTs | Bram        | LMS     | FIR     |

|             | Mul | Mac | Prod | Prod | Div | %           | %    | No (of)     | Mflop/s | Mflop/s |

| kc705_bist  |     |     |      |      |     | 7           | 15   | 63 (445)    |         |         |

| (8x)        |     |     |      |      |     |             |      |             |         |         |

| fp12_1x8_10 | 8x  |     |      |      | 1x  | 17          | 45   | 303 (445)   |         |         |

| (8x)        |     |     |      |      |     |             |      |             |         |         |

| fp12_1x8_20 | 8x  | 8x  |      |      | 1x  | 19          | 48   | 303 (445)   |         |         |

| (8x)        |     |     |      |      |     |             |      |             |         |         |

| fp12_1x8_30 | 8x  | 8x  | 8x   |      | 1x  | 21          | 55   | 303 (445)   |         |         |

| (8x)        |     |     |      |      |     |             |      |             | (8x)    | (8x)    |

| fp12_1x8_40 | 8x  | 8x  | 8x   | 1x   | 1x  | 21          | 56   | 303 (445)   | 1012    | 1403    |

Figure 4: Resources used by MicroBlaze and 8x (8xSIMD) EdkDSP, with FP division

The kc705\_bist design describes resources used by the MicroBlaze SoC without EdkDSP accelerators. The internal block RAM memory is set to 32 KB and 128 KB. Please, notice, that the Xilinx reference kc705\_bist design [2] works with internal block RAM memory set to 32 KB and 1 MB.

All designs with EdkDSP accelerators (fp11 and fp12) work with

- 64 single precision 3-stage pipelined floating point add/sub units each performing up to 175 MFLOP/s

- 64 single precision 4-stage pipelined floating point multiply units each performing up to 175 MFLOP/s

- 8 PicoBlaze6 controllers with 175 MHz system clock, each executing 87,5 Mil. instructions/s

- The 100 MHz MicroBlaze performance optimized processor is using one single precision 3-stage pipelined floating point add/sub unit and one single precision 4-stage pipelined floating point multiply unit, 32 KB data cache and 32 KB instruction cache.

The fp12 designs work in addition with

• 8 single precision 16-stage pipelined floating point divide units each performing up to 175 MFLOP/s. Designs use accelerators with different HW supported operation. This is reflected in the difference of resources used by the designs. See Figure 3 and Figure 4.

9/61

## 2.3 Use of external DDR3 memory

Presented FPGA designs are running on the Xilinx KC705 development board [1], [2]. See Figure 1. It is using the 1 GB DDR3 memory with clock signal 800 MHz. The DDR3 is connected to Xilinx Kintex7 xc7k325t-2 FPGA by 64 bit wide data path. The maximal theoretical peak performance of this external DDR3 memory with 800 MHz clock is therefore 1600(DDR2 transactions) x 8(bytes) = 12,8 GB/s. This is 102,4 Gb/s.

## 2.4 Re-programmability of EdkDSP accelerators

Each (8xSIMD) EdkDSP floating point accelerator subsystem contains one reprogrammable Xilinx PicoBlaze6 8-bit controller and the floating point (8xSIMD) DSP unit. The performance of the accelerator is application specific. In this demo, a single (8xSIMD) EdkDSP unit is delivering sustained 1403 MFLOP/s in case of 2000 tap FIR filter computation and 1012 MFLOP/s in case of the adaptive 2000 tap LMS filter identification demo. All designs have eight (8xSIMD) EdkDSP units.

The Xilinx PicoBlaze6 processor has fixed configuration with size of the program memory 4096 (18 bit wide) words, 64 Bytes scratch pad RAM memory and the interrupt vector in the address 1023.

The (8xSIMD) EdkDSP accelerator works with 2 program memories. Each program memory has 4096 (18bit wide) words. Both program memories are accessible by MicroBlaze processor via AXI-lite bus. The MicroBlaze application can write new firmware to the currently unused program memory, while the PicoBlaze6 is executing firmware from the second program memory.

The peak performance of data memories of all 8 (8xSIMD) EdkDSP accelerators in the included evaluation designs is 175 MHz (clock) x 4(bytes) x 3(mems) x 8(simd) x 8(instances) = 134,4 GB/s. This is 1075,2 Gb/s.

## 2.5 Debug of evaluation designs with EdkDSP accelerators

All EdkDSP accelerators can communicate with MicroBlaze program. The communication is using the Worker Abstraction Layer (WAL) library API. This API is used for support of writing of the debug information from the worker to the MicroBlaze terminal.

The PicoBlaze6 processors [5] can exchange data and text via the 8 bit communication data path with the MicroBlaze processor. This path is used to communicate parameters to the accelerators and to get messages or reports from accelerators for debugging. Text file with information from the accelerator can be stored in the RAM based file system of MicroBlaze. It can be downloaded to PC via Ethernet for inspection.

Floating point data are accessed by the MicroBlaze processor via the dual ported block memories of accelerators. The MicroBlaze side of the dual-ported memories is mapped into the MicroBlaze memory. The MicroBlaze processor can copy data from the dual ported memories to the DDR3 global workspace and display floating point data in the debugger. The computation in the (8xSIMD) EdkDSP units can overlap with the communication with the DDR3 performed by MicroBlaze. It is supported by data and program cache.

A Ping-Pong swap of memory banks is used by the accelerator firmware. The (8xSIMD) EdkDSP firmware is computing (in parallel) in some banks of all dual ported memories and the MicroBlaze is communicating (sequentially) to/from DDR3 in another set of banks of the dual-ported memories. This process can be stopped, inspected and debugged by the MicroBlaze debugger from the SDK 2013.4.

10/61

## 3. Installation and use of the evaluation package

## 3.1 Import of precompiled HW and SW projects into Xilinx SDK 2013.4

Unzip the evaluation package to directory of your choice. The directory c:\VM\_07 will be used in this application note. You will get these directories:

c:\VM\_07\d\_34\_7k

| 01.11.2014 16:11 | <dir></dir> |                          |

|------------------|-------------|--------------------------|

| 01.11.2014 16:11 | <dir></dir> |                          |

| 01.11.2014 16:09 | <dir></dir> | d_7k325t_fp11_6x8        |

| 01.11.2014 16:09 | <dir></dir> | d_7k325t_fp11_6x8_IMPORT |

| 01.11.2014 16:12 | <dir></dir> | d_7k325t_fp11_6x8_v1_10b |

| 01.11.2014 16:12 | <dir></dir> | d_7k325t_fp11_6x8_v1_20b |

| 01.11.2014 16:12 | <dir></dir> | d_7k325t_fp11_6x8_v1_30b |

| 01.11.2014 16:12 | <dir></dir> | d_7k325t_fp11_6x8_v1_40b |

| 01.11.2014 16:10 | <dir></dir> | d_7k325t_fp12_6x8        |

| 01.11.2014 16:10 | <dir></dir> | d_7k325t_fp12_6x8_IMPORT |

| 31.10.2014 14:25 | <dir></dir> | d_7k325t_fp12_6x8_v1_10b |

| 31.10.2014 14:24 | <dir></dir> | d_7k325t_fp12_6x8_v1_20b |

| 31.10.2014 14:24 | <dir></dir> | d_7k325t_fp12_6x8_v1_30b |

| 31.10.2014 14:23 | <dir></dir> | d_7k325t_fp12_6x8_v1_40b |

Select SDK 2013.4 workspace in c:\VM\_07\d\_34\_7k\d\_7k325t\_fp12\_6x8\SDK\_Workspace. See Figure 5.

| 🐽 Workspace Launcher                                                                                                  | ×         |

|-----------------------------------------------------------------------------------------------------------------------|-----------|

| Select a workspace                                                                                                    |           |

| Xilinx SDK stores your projects in a folder called a workspace.<br>Choose a workspace folder to use for this session. |           |

| Workspace: C:\VM_07\d_34_7k\d_7k325t_fp12_8x8\SDK_Workspace                                                           | Browse    |

| Use this as the default and do not ask again                                                                          |           |

|                                                                                                                       | OK Cancel |

Figure 5: Select the SDK Workspace

Add c:\VM\_07\d\_34\_7k\d\_7k325t\_fp12\_6x8\repo\_edkdsp path to the UTIA EdkDSP repository. See Figure 6.

| 🐵 Preferences                                                     |                                                                                                                                                                                                                                                                                                                                         | _ 🗆 🗵                                    |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| type filter text                                                  | Add, remove or change the order of SDK's software repositories.                                                                                                                                                                                                                                                                         | $\leftarrow \bullet \to \bullet \bullet$ |

| ⊕ · General<br>⊕ · C/C++                                          | Local Repositories (available to the current workspace)                                                                                                                                                                                                                                                                                 |                                          |

| Help     Install/Update     Remote Systems     Run/Debug     Team | C:\VM_07\d_34_7k\d_7k325t_fp12_8x8\edkdsp_repos                                                                                                                                                                                                                                                                                         | New<br>Remove                            |

| ···· Terminal<br>⊡·· Xilinx SDK                                   |                                                                                                                                                                                                                                                                                                                                         | Down                                     |

| Boot Image<br>Flash Programming                                   |                                                                                                                                                                                                                                                                                                                                         | Relative                                 |

| ···· Hardware Specification                                       | Global Repositories (available across workspaces)                                                                                                                                                                                                                                                                                       |                                          |

| ···· Log Information Level<br>···· Repositories                   |                                                                                                                                                                                                                                                                                                                                         | New                                      |

| XMD Startup                                                       |                                                                                                                                                                                                                                                                                                                                         | Remove                                   |

|                                                                   |                                                                                                                                                                                                                                                                                                                                         | Up                                       |

|                                                                   |                                                                                                                                                                                                                                                                                                                                         | Down                                     |

|                                                                   | SDK Installation Repositories         C:\pf\Xilinx\SDK\2013.4\sw\lib\         C:\pf\Xilinx\SDK\2013.4\sw\XilinxProcessorIPLib\         C:\pf\Xilinx\SDK\2013.4\sw\ThirdParty\         Rescan Repositories         Note: Local repository settings take precedence over global repository settings.         Restore Defaults       Apply |                                          |

| ?                                                                 | ОК                                                                                                                                                                                                                                                                                                                                      | Cancel                                   |

## Figure 6: Include the UTIA EdkDSP Repository

Click on the "Rescan Repositories" button. Click on the "Apply button", and finally click on the OK button. The path to the SW drivers has been defined.

In SDK, select File -> New -> Project ... -> Xilinx -> Hardware Platform Specification. See Figure 7. Click on the Next button.

| 🐵 New Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |        |        |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|

| Select a wizard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |        |        |        |

| Wizards:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |        |        |        |

| type filter text                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |        |        |        |

| General  C/C++ C/ |        |        |        |        |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | < Back | Next > | Finish | Cancel |

#### *Figure 7: Specify the hardware platform*

In the "New Hardware Project" screen, fill into the Project name: hw\_platform\_0 In the New Hardware Project screen, fill into the Target Hardware Specification:

#### $c:\\M_07\d_34_7k\d_7k325t_fp12_6x8_v1_40b\SDK\SDK_Export\hw\system.xml$

This will specify one of the 8 precompiled HW designs present in the evaluation package. See Figure 8.

We have selected the **d\_7k325t\_fp12\_6x8\_v1\_40b** design, demonstrating the use of eight instances the UTIA EdkDSP accelerators, all with 8xSIMD data path, with floating point single data path division. All eight (8xSIMD) accelerators compiled in this design have identical capabilities defined by the IP core: bce\_fp12\_1x8\_0\_axiw\_v1\_40\_b.

Click on "Finish" button to finalize the selection of the precompiled HW design. See Figure 8.

| 🐵 New Hardware Project                                                                                                                                                                                                                        |                                        |                                       |                 |                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------|-----------------|----------------------|

| New Hardware Project<br>Create a new Hardware Project.                                                                                                                                                                                        |                                        |                                       |                 |                      |

| Project name: hw_platform_0                                                                                                                                                                                                                   |                                        |                                       |                 |                      |

| Use default location Location: C:\VM_07\d_34_7k\d_7k325t_fp12_8xi Choose file system: default 💌                                                                                                                                               | 8\SDK_Workspa                          | ce\hw_platform_(                      | 0               | Browse               |

| Target Hardware Specification<br>Provide the path to the hardware specification file<br>This file usually resides in SDK/SDK_Export/hw fol<br>The specification file and associated bitstream con<br>C:\VM_07\d_34_7k\d_7k325t_fp11_8x8_v1_40 | der relative to t<br>ntent will be cop | he XPS/Vivado pr<br>ied into the work | oject location. | do or IPI.<br>Browse |

| <ul> <li>Bitstream and BMM Files</li> </ul>                                                                                                                                                                                                   |                                        |                                       |                 |                      |

|                                                                                                                                                                                                                                               |                                        |                                       |                 |                      |

|                                                                                                                                                                                                                                               |                                        |                                       |                 |                      |

| ?                                                                                                                                                                                                                                             | < Back                                 | Next >                                | Finish          | Cancel               |

*Figure 8: Use the name "hw\_platform\_0" and select one of the provided xml design descriptions*

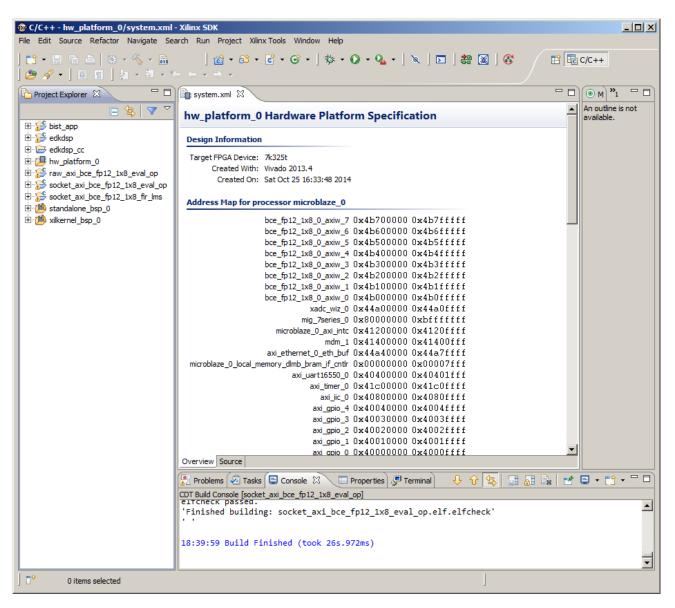

SDK is interpreting the system.xml and presents HW cores of in the design. See Figure 9.

The hardware platform "hw\_platform\_0" has been created.

| C/C++ - hw_platform_0/system.xml - Xilin              | x SDK                                                                                                                   | _ [D] ×                       |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| File Edit Source Refactor Navigate Search             |                                                                                                                         |                               |

|                                                       |                                                                                                                         |                               |

|                                                       | • 🗳 • 🗳 • 🕉 •   🏇 • 💽 • 🎭 •   🔌   🖂   🏶 📓   🚱 /                                                                         | 🖇 🔹 🔛 📴 C/C++                 |

| ] <b>□ □ ] 2</b> • 7 • ← • → •                        |                                                                                                                         |                               |

| Project Explorer                                      | system.xml 🛛                                                                                                            |                               |

|                                                       | hw_platform_0 Hardware Platform Specification                                                                           | An outline is not available.  |

| □ <sup>7</sup> hw_platform_0<br>system_wrapper_bd.bmm | Design Information                                                                                                      |                               |

| system_wrapper.bit                                    | Tarast EDCA Davisar 7/225t                                                                                              |                               |

| system.xml                                            | Target FPGA Device: 7k325t<br>Created With: Vivado 2013,4                                                               |                               |

|                                                       | Created On: Sat Oct 25 16:33:48 2014                                                                                    |                               |

|                                                       | Created On. 3at Oct 23 10.33.46 2014                                                                                    |                               |

|                                                       | Address Map for processor microblaze_0                                                                                  |                               |

|                                                       | bce_fp12_1x8_0_axiw_7_0x4b700000_0x4b7fffff                                                                             |                               |

|                                                       | bce_fp12_1x8_0_axiw_6 0x4b600000 0x4b6fffff                                                                             |                               |

|                                                       | <pre>bce_fp12_1x8_0_axiw_5 0x4b500000 0x4b5fffff</pre>                                                                  |                               |

|                                                       | bce_fp12_1x8_0_axiw_4 0x4b400000 0x4b4fffff                                                                             |                               |

|                                                       | bce_fp12_1x8_0_axiw_3 0x4b300000 0x4b3fffff                                                                             |                               |

|                                                       | bce_fp12_1x8_0_axiw_2 0x4b200000 0x4b2fffff                                                                             |                               |

|                                                       | <pre>bce_fp12_1x8_0_axiw_1 0x4b100000 0x4b1fffff</pre>                                                                  |                               |

|                                                       | bce_fp12_1x8_0_axiw_0 0x4b000000 0x4b0fffff                                                                             |                               |

|                                                       | xadc_wiz_0 0x44a00000 0x44a0fff                                                                                         |                               |

|                                                       | mig_7series_0 0x80000000 0xbfffffff<br>microblaze 0 axi intc 0x41200000 0x4120ffff                                      |                               |

|                                                       | mdroblaze_0_ax_intc 0x41200000 0x41201111<br>mdm_1 0x41400000 0x41400fff                                                |                               |

|                                                       | axi ethernet 0 eth buf 0x44a40000 0x44a7ffff                                                                            |                               |

|                                                       | microblaze_0_local_memory_dlmb_bram_if_cntr 0x00000000 0x00007fff                                                       |                               |

|                                                       | axi_uart16550_0 0x40400000 0x40401fff                                                                                   |                               |

|                                                       | axi timer 0 0x41c00000 0x41c0fff                                                                                        |                               |

|                                                       | axi_iic_0 0x40800000 0x4080ffff                                                                                         |                               |

|                                                       | axi_gpio_4 0x40040000 0x4004ffff                                                                                        |                               |

|                                                       | axi_gpio_3 0x40030000 0x4003ffff                                                                                        |                               |

|                                                       | axi_gpio_2 0x40020000 0x4002ffff                                                                                        |                               |

|                                                       | axi_gpio_1 0x40010000 0x4001ffff                                                                                        |                               |

|                                                       | axi_gpio_0 0x4000000 0x4000ffff                                                                                         | <b>_</b>                      |

|                                                       | Overview Source                                                                                                         |                               |

|                                                       | 🖹 Problems 🖉 Tasks 🖳 Console 🛛 🔲 Properties 🖉 Terminal                                                                  | 📑 🔓 🛃 🗄 🖆 🗐 🗸 🔂 🖬 🗖           |

|                                                       | SDK Log                                                                                                                 |                               |

|                                                       | 16:55:23 INFO : Reading in cores from local repositories:                                                               | <u> </u>                      |

|                                                       | C:\VM_07\d_34_7k\d_7k325t_fp12_8x8\edkdsp_repos<br>16:55:23 INFO : Updating libgen.options on all BSP projects.         |                               |

|                                                       | 16:55:23 INFO : Updating libgen.options on all BSP projects.<br>16:55:23 INFO : Cleaning BSP projects in the workspace. |                               |

|                                                       | 16:55:34 INFO : Saving repository preferences.                                                                          |                               |

|                                                       | 17:01:43 INFO : Project 'hw_platform_0' created. You can now creat                                                      | e BSPs and application projec |

|                                                       |                                                                                                                         |                               |

|                                                       |                                                                                                                         |                               |

|                                                       |                                                                                                                         |                               |

| , u                                                   | 1                                                                                                                       |                               |

### Figure 9: Hardware platform with the MicroBlaze processor and the address map

SW projects can be imported into SDK now. Select:

File -> Import -> General -> Existing Projects into Workspace Click on Next button. See Figure 10.

http://zs.utia.cas.cz

15/61

| 🐵 Import                                                         |        |

|------------------------------------------------------------------|--------|

| Select<br>Create new projects from an archive file or directory. | è      |

| Select an import source:<br>type filter text                     |        |

| Back Next > Finish                                               | Cancel |

#### Figure 10: Import existing projects into workspace

Select the directory with projects to be imported. See Figure 11.

#### c:\VM\_07\d\_34\_7k\d\_7k325t\_fp12\_6x8\_IMPORT

Set the "Copy projects into workspace" check box. Click on Finish button. See Figure 11.

http://zs.utia.cas.cz

| 🕸 Import                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _ 🗆 🗙  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|--|--|

| Import Projects<br>Select a directory to search for existing Edipse projects.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |  |  |  |  |  |  |

| Select root directory: C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT     Select archive file: Projects:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |  |  |  |  |  |  |

| <ul> <li>bist_app (C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT\bist_app)</li> <li>edkdsp (C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT\edkdsp)</li> <li>edkdsp_cc (C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT\edkdsp)</li> <li>raw_axi_bce_fp12_1x8_eval_op (C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT\raw_axi_bce_fp12_1x8_eval_op)</li> <li>socket_axi_bce_fp12_1x8_eval_op (C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT\socket_axi_bce_fp12_1x8_eval_op)</li> <li>socket_axi_bce_fp12_1x8_eval_op (C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT\socket_axi_bce_fp12_1x8_eval_op)</li> <li>socket_axi_bce_fp12_1x8_fr_lms (C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT\socket_axi_bce_fp12_1x8_fr_lms)</li> <li>standalone_bsp_0 (C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT\standalone_bsp_0)</li> <li>xilkernel_bsp_0 (C:\VM_07\d_34_7k\d_7k325t_fp12_8x8_IMPORT\xilkernel_bsp_0)</li> </ul> |        |  |  |  |  |  |  |

| Copy projects into workspace Working sets Working sets:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Select |  |  |  |  |  |  |

| <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Cancel |  |  |  |  |  |  |

#### Figure 11: Select copy projects into workspace and finish the import of all projects.

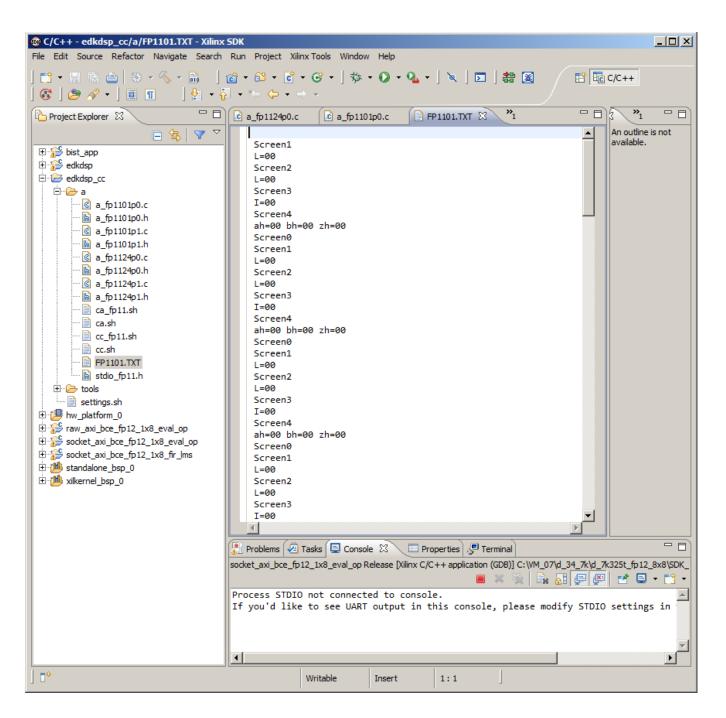

All the UTIA EdkDSP SW projects are imported into SDK workspace from the directory c:\VM\_07\d\_34\_7k\d\_7k325t\_fp12\_6x8\_IMPORT

Process of compilation will start automatically. This first compilation of all SDK SW projects can take several minutes to finish. It should finish without errors. See Figure 12.

17/61

http://zs.utia.cas.cz

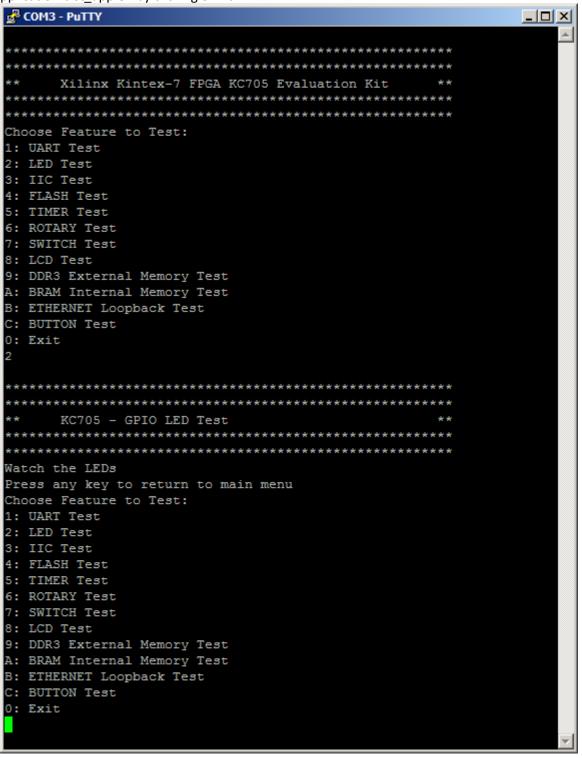

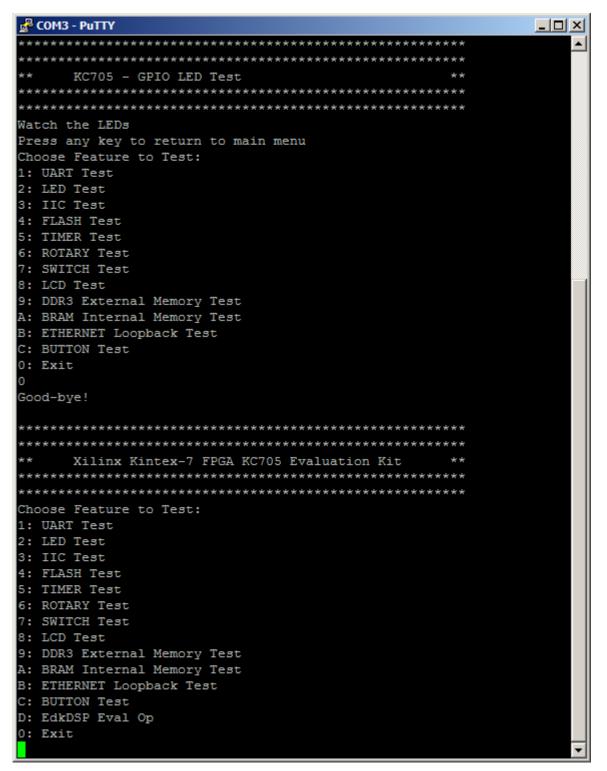

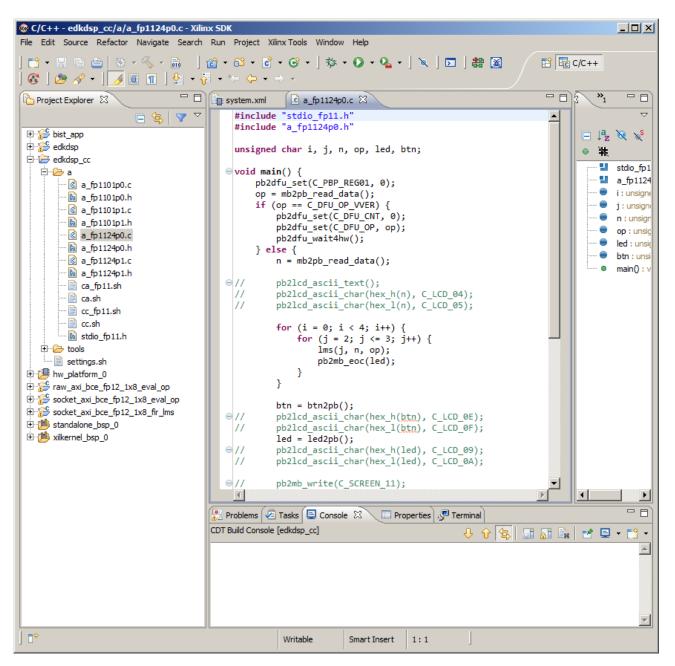

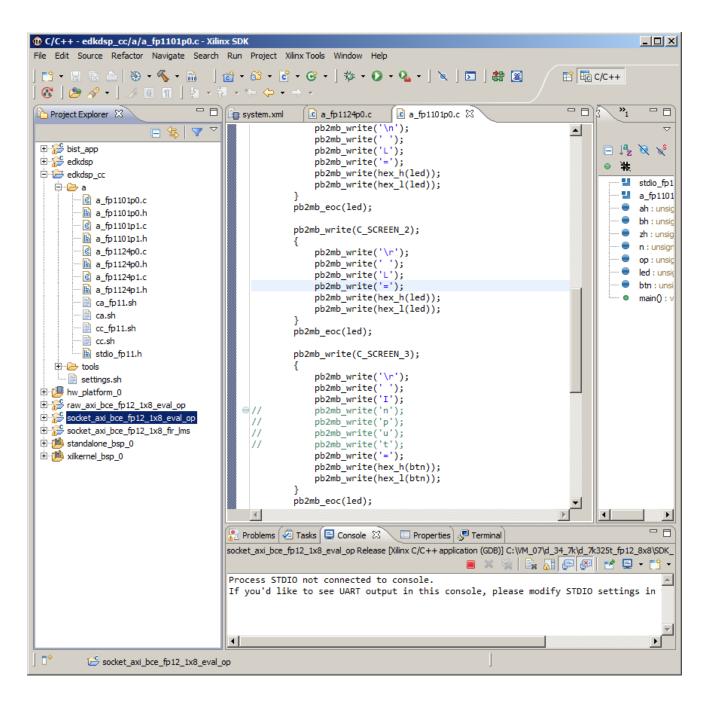

## 3.2 Evaluation of demo projects

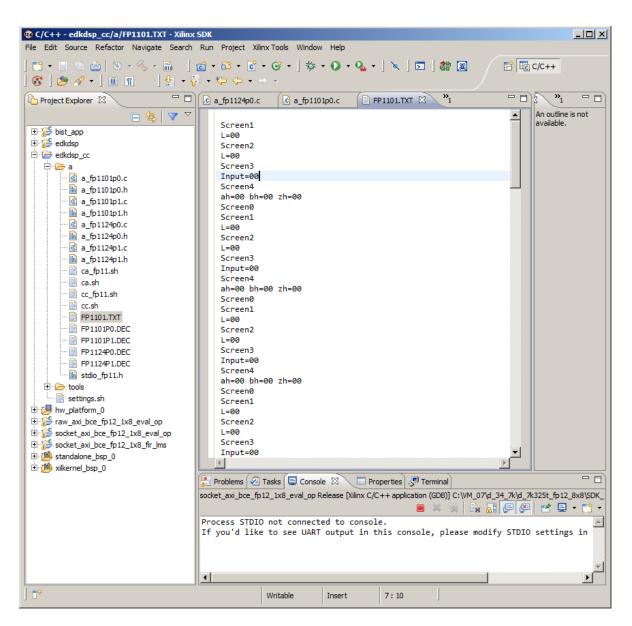

The "bist\_app" project in the "Project Explorer" window of the SDK 2013.4 is only slightly modified version of the Xilinx BIST SW application project. The RAM memory test is adjusted for the 128 KB RAM. See Figure 12.

The "edkdsp" project is extending the "bist\_app" with tests of the EdkDSP accelerator, without Ethernet.

The "raw\_axi\_bce\_fp12\_1x8\_eval\_op" project is extending the "edkdsp" with RAW version of the lwIP Ethernet www server GUI, the TFTP file server and the RAM based file system.

The "socket\_axi\_bce\_fp12\_1x8\_eval\_op" project is extending the "edkdsp" with SOCKET version of the IwIP Ethernet www server GUI, the TFTP file server and the RAM based file system.

The "socket\_axi\_bce\_fp12\_1x8\_fir\_lms" project is demonstrating the floating point FIR filter and LMS filter computation on a single (8xSIMD) EdkDSP accelerator with the SOCKET version of the IwIP Ethernet www server GUI, the SOCKET version of the TFTP file server and the RAM based file system.

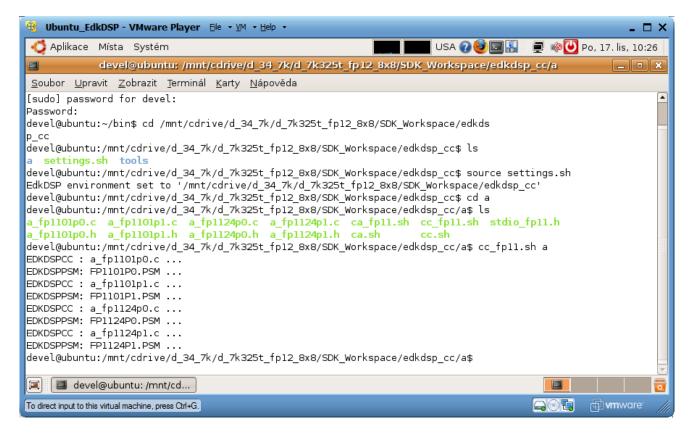

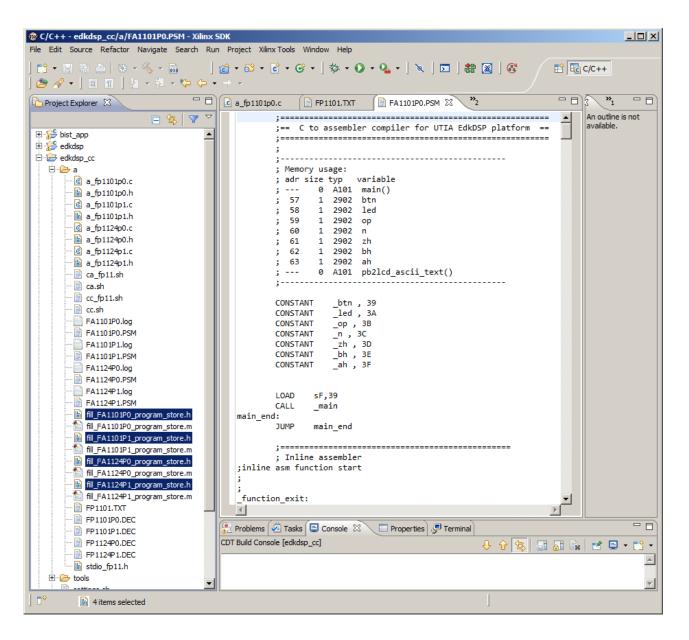

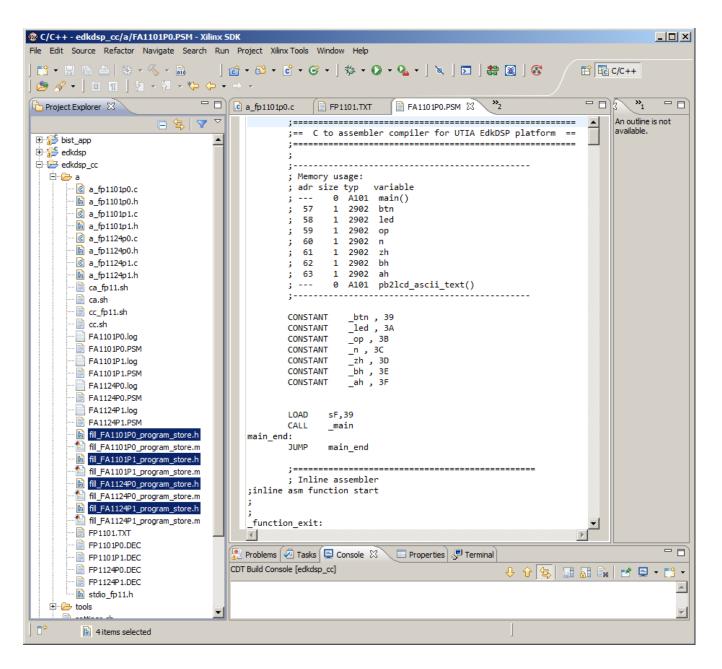

Figure 12: All projects are compiled. See IP blocks present in the design.

Connect the jtag and serial line USB cables to your KC705 board. Switch ON the board.

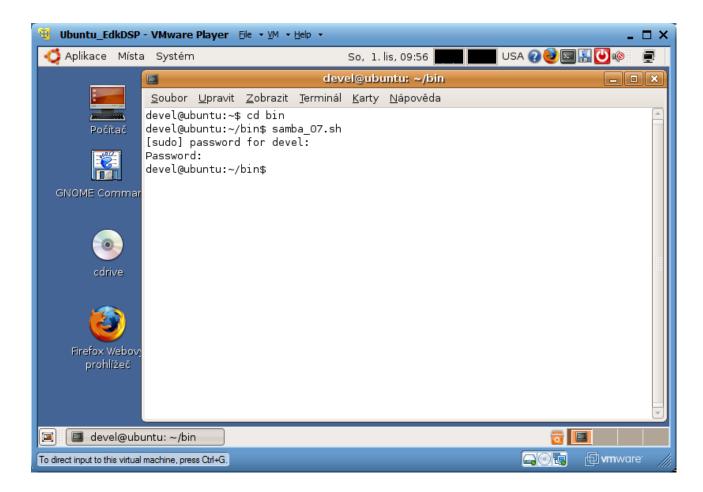

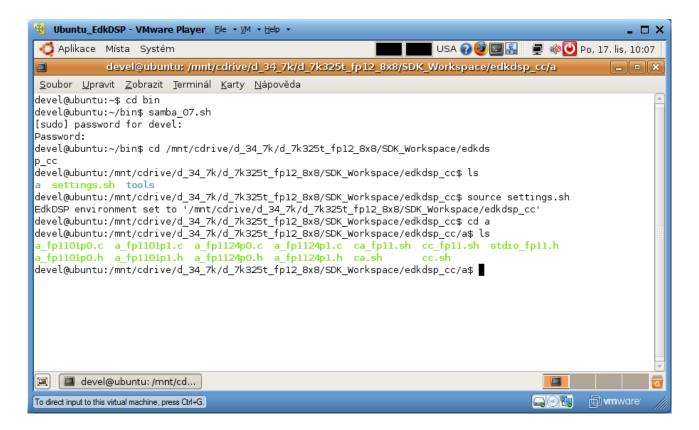

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | earch Run Project Xilinx Tools Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |